At the SSCD group, IIT Kanpur, we explore a wide range of research areas, with some key focus topics highlighted below:

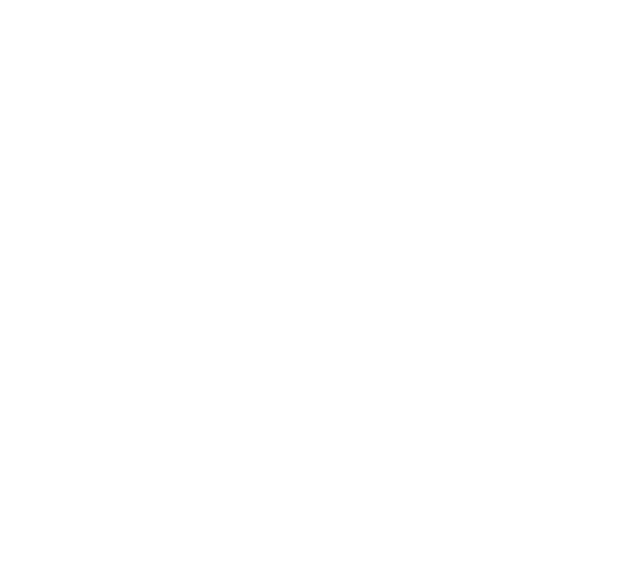

Radio Frequency Receivers

Delay lines

LNAs

Mixers

RF Filters

Power Amplifiers

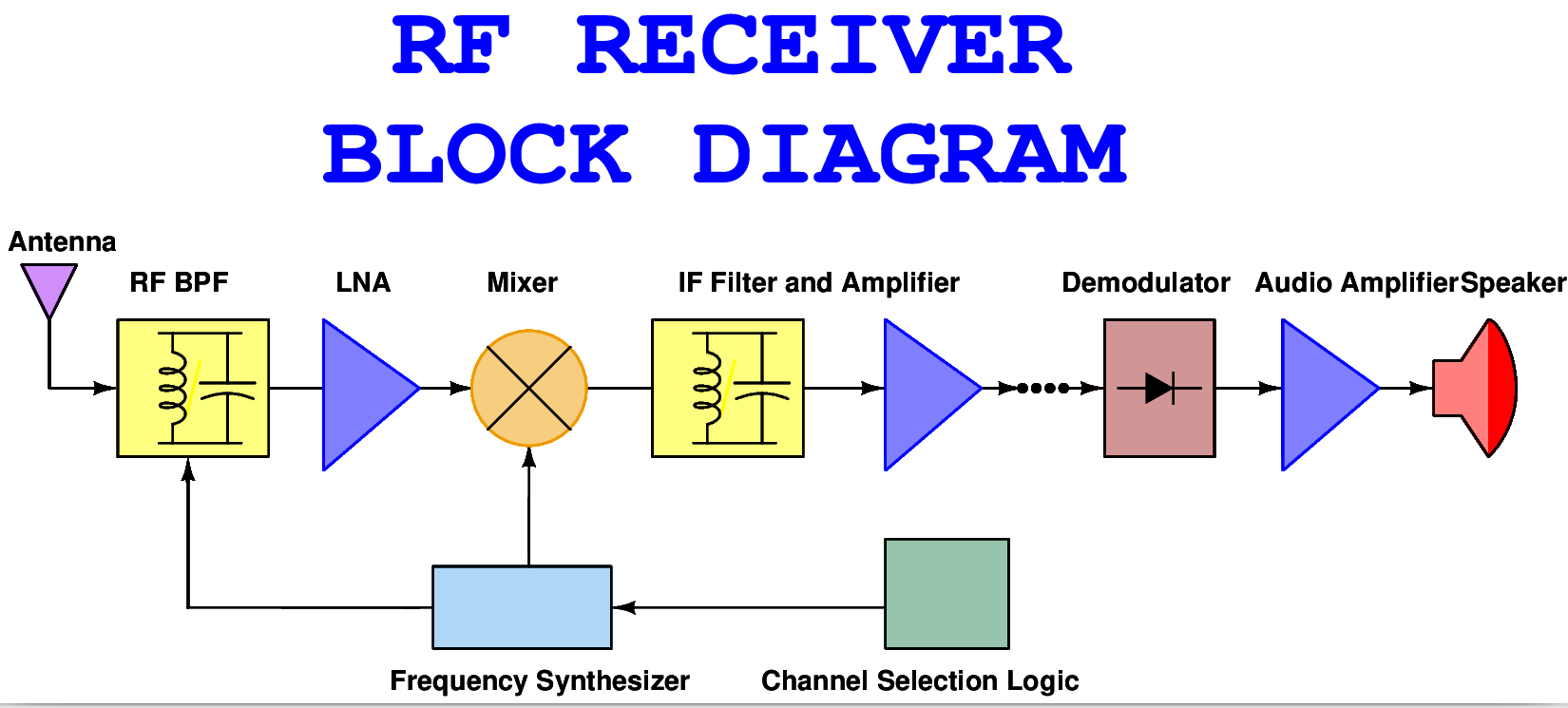

Data converters

Delta-sigma modulators

SAR ADCs

Flash ADCs

Comparators

Digital to analog converters

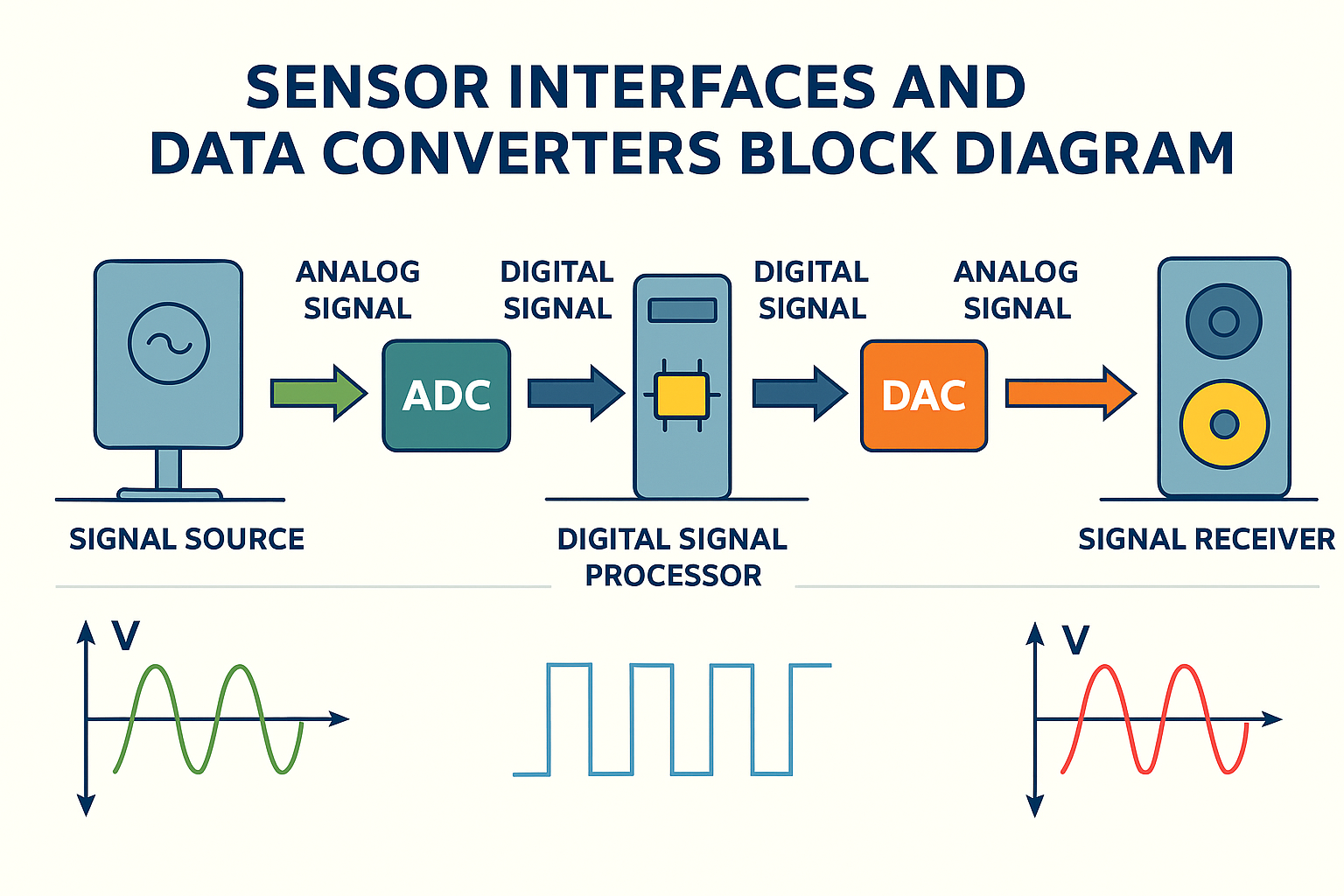

Frequency synthesizers

PLLs

DLLs

Loop filters

Oscillators

Time to digital converters

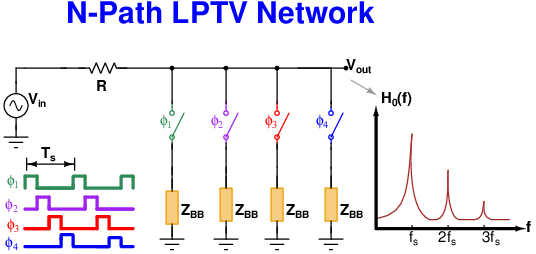

N-Path networks

LPTV networks

N-path filters

Mixer first receivers

LPTV delay lines

Research Workflow in Integrated Circuit (IC) Design in our lab.

Identifying a key research problem.

Propose a novel solution (either at the circuit level or at the system level or, both).

Simulate and verify the idea through top-level validation.

Design a prototype integrated circuit and send it for fabrication.

Develop a printed circuit board (PCB) for chip integration and testing.

Test and characterize the fabricated chip to corroborate the proposed idea with the measured results from the chip!

A successful chip usually finds its way to a good journal or a conference!