- Admissions 2026-27 Semester-I Announcements New

- Admission Notice under Joint PhD with University of Melbourne in Quantum communications New

- IIT Kanpur Certificate Program on PYTHON for Artificial Intelligence Machine Learning and Deep Learning, 15th June to 15th July 2026 New

- Applied Data Science & Machine Intelligence: Fundamentals to Next Generation AI: 1st June to 15th July 2026 New

- IIT Kanpur Certificate Program on Python QISKIT for Data Science, Data Analytics, Machine Learning (ML) and Quantum Computing, 1st March to 27th March 2026 New

- Notice for Spot PhD Admissions

- The IEEE DEIS Summer School 2025 on the theme of 'Insulating and Multifunctional Dielectrics' was hosted for the first time in India, at IIT Kanpur, from 20th to 25th September.

- IIT KANPUR Certificate Program on PYTHON + MATLAB/ OCTAVE-Based Simulation and Design of 5G/ 6G Wireless Technologies, 1st September to 26th September 2025

- Dr. Meena Mishra, DRDO graced us as the Guest of Honour for the 58th Convocation.

- Farewell to the class of 2025 organized by EEA on 22nd April 2025

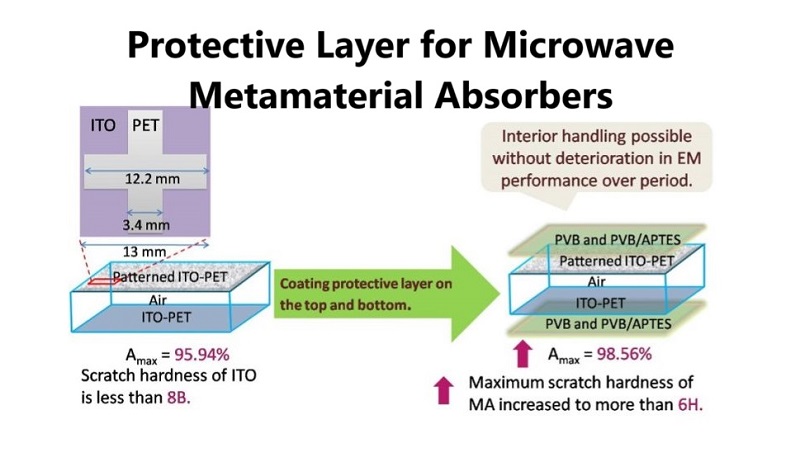

- Workshop on "Metamaterial Antennas and Applications" was successfully conducted from April 18-20 2025, coordinated by Prof. Raghvendra Kumar Chaudhary and Prof. Kumar Vaibhav Srivastava

- Invited Lecture by Prof. Akhilesh Jaiswal (University of Wisconsin-Madison, USA) titled "Unconventional Computing Paradigms from Extreme-Edge to Extreme-Scale" was successfully conducted on 15th April 2025

- EMI/EMC (Electromagnetic Interference and Compatibility) and Electrical Safety Test Facility, accredited by National Accreditation for Testing and Calibration Laboratories (NABL) was launched on 5 April, 2025 at IIT Kanpur under the leadership of Prof. M. Jaleel Akhtar

- Happy Hours for UG students organized by EEA on 24th March 2025

- Invited Lecture by Prof. Souvik Mahapatra (IIT Bombay) titled “A Device (TCAD) to Circuit (SPICE) Framework for BTI and HCD Aging” was successfully conducted on 24th February 2025

- Lecture by Prof. Saurabh Lodha (IIT Bombay) titled “Engineering the strain and neuromorphic performance of 2D-TMD transistors” was successfully conducted on 25th February 2025

- Invited Lecture by Mr. Milind Dhighrasker, Senior Director, ON Semiconductors titled “Overview of Design Challenges for SiC-based Traction Inverters” on 31st January 2025

- Invited Lecture by Prof. William G. Whittow, Wolfson School of Mechanical, Electrical and Manufacturing Engineering (WSMEME) at Loughborough University titled “Recent Advances in Reconfigurable RF Frontend Systems” was successfully conducted on 6th January 2025

- Bonfire Evening - Relive the Joys of College Days organized by EEA on 4th January 2025

- Invited Lecture by Prof. Srabanti Chowdhury (Stanford university) titled “Unleashing the Potential of Wideband Gap Materials” was successfully conducted on 2nd January 2025

Admissions 2026-27 Semester-I Announcements Read More...

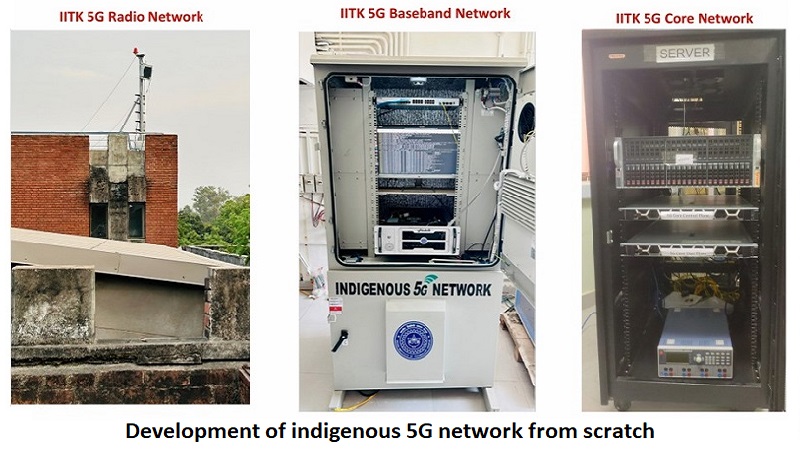

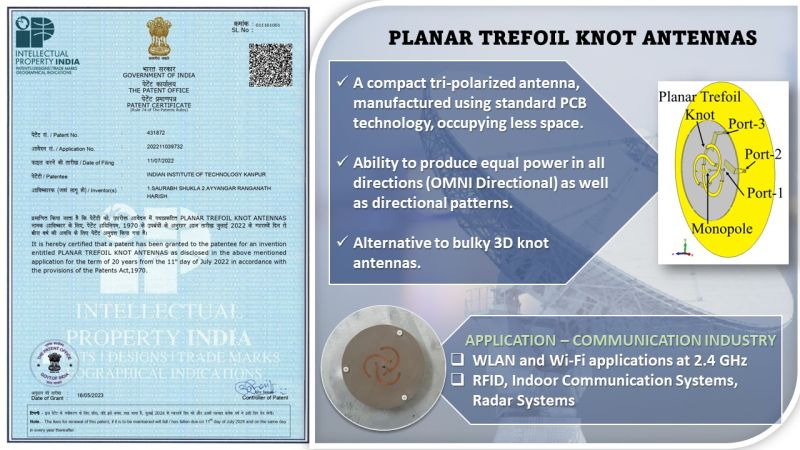

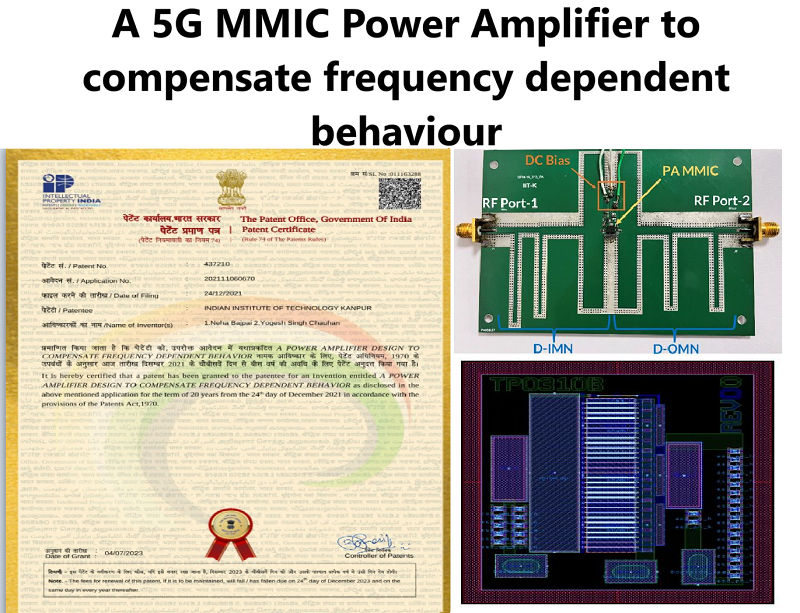

Welcome to the Department of Electrical Engineering (EE) at IIT Kanpur. The EE department is one of the oldest departments at IIT Kanpur. It was one of the first five departments with which IIT Kanpur started in 1960. Subsequently, the Advanced Centre for Electronics Systems (ACES) came into existence in early 1970 by a grant from the Ministry of Defence to undertake manpower training and to carry out research and development related to defense. Subsequently, several sponsored projects in many subject areas with large interdisciplinary content were handled through ACES. ACES is now an integral part of the EE department and houses the majority of EE laboratories and facilities. The department is currently the largest multidisciplinary department at IIT Kanpur. It covers practically all sub-disciplines in Electrical and Communication Engineering including Power Systems, Power Electronics, Microwaves, RF techniques, Microelectronics, VLSI, Photonics, Control Systems, Robotics, Speech, and Audio Processing, Computer Vision, Artificial Intelligence, Machine Learning, Wireless Communication, Computer Networks, Future wireless networks like 5G/6G, Wireless sensor networks, and IoT networks. Read more

Welcome to the Department of Electrical Engineering (EE) at IIT Kanpur. The EE department is one of the oldest departments at IIT Kanpur. It was one of the first five departments with which IIT Kanpur started in 1960. Subsequently, the Advanced Centre for Electronics Systems (ACES) came into existence in early 1970 by a grant from the Ministry of Defence to undertake manpower training and to carry out research and development related to defense. Subsequently, several sponsored projects in many subject areas with large interdisciplinary content were handled through ACES. ACES is now an integral part of the EE department and houses the majority of EE laboratories and facilities. The department is currently the largest multidisciplinary department at IIT Kanpur. It covers practically all sub-disciplines in Electrical and Communication Engineering including Power Systems, Power Electronics, Microwaves, RF techniques, Microelectronics, VLSI, Photonics, Control Systems, Robotics, Speech, and Audio Processing, Computer Vision, Artificial Intelligence, Machine Learning, Wireless Communication, Computer Networks, Future wireless networks like 5G/6G, Wireless sensor networks, and IoT networks. Read more

Admissions - 2026-27 Semester I

Announcements

16 March 2026:

PhD Position in Quantum Communications for 6G Networks

Applications are invited for a Joint PhD position between the Indian Institute of Technology Kanpur (IITK) and the University of Melbourne (UoM) under the Melbourne India Postgraduate Academy (MIPA) program.

This PhD project focuses on Quantum Communications in the context of next-generation (6G) communication networks.

Program Overview

The selected candidate will be enrolled as a joint PhD student at both IIT Kanpur and the University of Melbourne. The student will spend approximately 1–2 years at each institution, benefiting from the research environment and expertise at both universities. Learn more about the MIPA program:

Research Topic

The project will focus on the design and analysis of quantum communication protocols for future 6G networks. With the rapid evolution of communication infrastructure, there is a growing need for highly secure and scalable communication systems capable of supporting massive connectivity while ensuring privacy and security. Quantum communication paradigm including quantum key distribution (QKD) has emerged as a promising approach for enabling provably secure key exchange and communication. This project will explore how quantum communication technologies can be integrated with future wireless and optical communication networks to enable secure and scalable next-generation communication systems.

For details, please visit the following page at the university of Melbourne website.

Applicants should have a strong background in engineering, physics, or related fields. Prior exposure to quantum mechanics, photonics, communication systems, or information theory is desirable but not mandatory. Following students are encouraged to apply

- BTech/ MTech/ MS (Research) graduates

- Final-year students who expect to complete their degree before the program begins

Application Process

Interested candidates should email with their CV expressing their interest in the position to This email address is being protected from spambots. You need JavaScript enabled to view it. and This email address is being protected from spambots. You need JavaScript enabled to view it. .

- Details

- Last Updated: Friday, 20 March 2026 10:38

Manoj Kumar Garg (DST Inspire Faculty)

Manoj Kumar Garg (DST Inspire Faculty)

This email address is being protected from spambots. You need JavaScript enabled to view it.

+919518213581

ACES: 308 | Home Page

Shanuja Sasi (DST Inspire Faculty)

Shanuja Sasi (DST Inspire Faculty)

This email address is being protected from spambots. You need JavaScript enabled to view it.

+91-512-259-5499

ACES - 305A

- Details

- Last Updated: Thursday, 23 October 2025 15:52

- Details

- Last Updated: Thursday, 12 March 2026 15:58

- Details

- Last Updated: Wednesday, 04 February 2026 15:08

Engineering the strain and neuromorphic performance of 2D-TMD transistors

Abstract- In recent years, researchers have leveraged the unique physical properties of layered two-dimensional (2D) van der Waals (vdW) materials, such as a wide range of thickness-dependent bandgaps and facile fabrication of heterostructures with defect-free heterointerfaces, for several electronic applications. At the same time, their optical and electrical properties can be controlled using strain tuning of band structure parameters because of their high tensile strength, as well as via electrostatic gating based tuning of carrier concentrations because of their ultra-thin nature.

This presentation will first describe recent results from our group on engineering the strain-modulated performance of transistors based on 2D vdW transition metal dichalcogenide (TMD) semiconductors. Specifically, an electrically actuated piezo-stack is shown to fine-tune optical and electrical parameters of MoS2 field-effect transistors with tensile as well as compressive strain, offering improved control and integration possibilities over existing mechanical methods. [1] Next, we will describe the use of independent electrostatic gating of contact and channel barriers in 2D TMD transistors towards realizing neuronal spiking behaviour, closely mimicking biological neurons with functionalities such as spike- frequency adaptation and post-inhibitory rebound, at a low energy consumption of 3.5 pJ/spike. [2]

Bio: Prof. Saurabh Lodha is the P. K. Kelkar Chair Professor at the Department of Electrical Engineering, Indian Institute of Technology (IIT) Bombay in India. He graduated from IIT Bombay in 1999 with a B. Tech (EE) followed by a Masters (ECE) and PhD (ECE) from Purdue University, USA, in 2001 and 2004 respectively. From 2005-2010 he worked at Intel Corporation in Portland, USA, on the research and development of 45, 32 and 22 nm Si CMOS technologies. He joined IIT Bombay in 2010 where he is also the PI of the IITB-OSU Frontier Research Center. His research interests span devices and materials in the areas of advanced CMOS technologies, 2D (opto)electronics and gallium oxide power electronics. He has been awarded the Swarna Jayanti fellowship (2017) and the Young Career Award (2020) by the Department of Science and Technology, Govt. of India, and the KLC Memorial Distinguished Lecture Award (2023) by IIT Delhi.

Speaker Name: Prof. Saurabh Lodha

Professor, Department of Electrical Engineering, IIT Bombay, Powai, Mumbai, India, 400076

E-mail: This email address is being protected from spambots. You need JavaScript enabled to view it.

Date and Time: 25, February 2025 10:30 AM-12:00 PM

Venue: ACES 214, ACES building

- Details

- Last Updated: Thursday, 20 February 2025 09:05